Transistor a effetto di campo

In elettronica il transistor a effetto di campo (in inglese Field-Effect Transistor, abbreviato FET) è un tipo di transistor largamente usato nel campo dell'elettronica digitale, diffuso anche nell'elettronica analogica.

Si tratta di un substrato di materiale semiconduttore drogato, solitamente in silicio, al quale sono applicati quattro terminali: il gate, il source, il drain ed il bulk; quest'ultimo, se presente, è generalmente connesso al source e se non presente è connesso al terminale esterno del gate. Il principio di funzionamento del transistor ad effetto di campo si fonda sulla possibilità di controllare la conduttività elettrica del dispositivo, e quindi la corrente elettrica che lo attraversa, mediante la formazione di un campo elettrico al suo interno. Il processo di conduzione coinvolge solo i portatori di carica maggioritari, pertanto questo tipo di transistore è detto unipolare.

La diversificazione dei metodi e dei materiali usati nella realizzazione del dispositivo ha portato alla distinzione di tre principali famiglie di FET: JFET, MESFET e MOSFET. Il JFET, abbreviazione di Junction FET, è dotato di una giunzione p-n come elettrodo rettificante; il MESFET, abbreviazione di Metal Semiconductor FET, una giunzione Schottky raddrizzante metallo-semiconduttore ed il MOSFET, abbreviazione di Metal-Oxide-Semiconductor FET, genera il campo elettrico grazie ad una struttura metallica esterna, separata dalla giunzione da uno strato di dielettrico.

Il transistor a effetto di campo è stato inventato da Julius Edgar Lilienfeld nel 1925, ma i primi dispositivi costruiti, i JFET, risalgono 1952, quando fu tecnologicamente possibile realizzarli. Il Fet più diffuso è il MOSFET, realizzato da Dawon Kahng e Martin Atalla nel 1959 presso i Bell Laboratories.[1] Insieme al transistor a giunzione bipolare, il FET è il transistor più diffuso in elettronica: a differenza del BJT esso presenta il vantaggio di avere il terminale gate di controllo isolato, nel quale non passa alcuna corrente

Struttura

[modifica | modifica wikitesto]

Il transistor ad effetto di campo viene realizzato affiancando il terminale di gate da due regioni di silicio drogate in maniera opposta al bulk, che costituiscono i terminali di drain e source. Tali diffusioni costituiscono una giunzione p-n, un contatto tra i blocchi di tipo P e di tipo N ed è priva di portatori liberi. Ai due lati della giunzione vi è una differenza di potenziale costante, chiamata tensione di built-in, che deve mantenere una polarizzazione inversa per il funzionamento del dispositivo.

La regione di substrato compresa tra i due terminali drain e source è detta regione di canale, ed è caratterizzata da una lunghezza di canale L e da una larghezza di canale W, misurate rispettivamente lungo la direzione parallela e perpendicolare rispetto al verso della corrente che percorre il canale. Tale regione fornisce un percorso conduttivo tra i due terminali ed è separata dal gate da un sottile strato solitamente composto da biossido di silicio.

Distribuzione delle cariche all'interno del semiconduttore

[modifica | modifica wikitesto]A seconda della tensione applicata ai capi del FET si verificano tre diverse configurazioni di carica all'interno del dispositivo, riportate di seguito nel caso di un substrato con drogaggio di tipo p:

Regione di accumulazione

[modifica | modifica wikitesto]La regione di accumulazione si verifica quando all'elettrodo di gate viene imposta una tensione negativa rispetto al bulk, generalmente posto a massa. In questa configurazione le lacune del substrato si accumulano in un piccolo strato in prossimità del terminale di gate: questa è la condizione di accumulazione.

Regione di svuotamento

[modifica | modifica wikitesto]La regione di svuotamento si verifica quando all'elettrodo di gate viene imposta una tensione positiva rispetto al bulk. In questa configurazione le lacune del substrato si allontanano dalla gate, lasciando una regione di svuotamento in prossimità di esso.

Regione di Inversione

[modifica | modifica wikitesto]La regione di inversione si verifica quando all'elettrodo di gate viene imposta una tensione positiva superiore ad una certa tensione, detta tensione di soglia. In questa configurazione gli elettroni presenti nel substrato vengono attratti dal gate, e se la tensione supera la tensione di soglia la concentrazione di elettroni in prossimità del terminale di gate è maggiore di quella delle lacune: si forma così uno strato di inversione nel quale il silicio è diventato drogato di tipo n.

Lo strato di inversione è molto sottile e l'elevata concentrazione di elettroni è spiegata dal processo di generazione elettrone-lacune nella regione di svuotamento.

Funzionamento

[modifica | modifica wikitesto]

In un transistor FET l'effetto transistor si ottiene tramite il campo elettrico indotto dalla tensione applicata tra il terminale di gate e l'estremità opposta del semiconduttore, detto bulk, che è generalmente posto al potenziale di source. Tale differenza di potenziale crea un canale di conduzione nel silicio attraverso il quale i portatori di carica si spostano dal source al drain nel caso di un FET a canale N, dal drain al source nel caso di un FET a canale P. L'applicazione di una tensione al gate permette quindi di controllare il passaggio di cariche tra il source e il drain, e quindi la corrente elettrica che attraversa il dispositivo.

Per un transistor FET a canale n la regione di substrato che collega drain e source, la regione di canale, può essere o ricca di lacune, o vuota, o ricca di elettroni a seconda che sia rispettivamente di accumulazione, di svuotamento o di inversione. Quando si applica una tensione superiore alla tensione di soglia tra i terminali di gate e source, ottenendo la regione di inversione, vi è un passaggio di cariche attraverso il canale controllato dalla tensione al terminale di gate. Se la tensione è invece inferiore alla tensione di soglia vi è il passaggio di una piccola corrente, detta corrente di sottosoglia.

Per un transistor FET a canale p, le distribuzioni di carica sono contrarie, per cui il substrato ha un drogaggio di tipo n e i terminali di gate e source di tipo p.

A seconda della tensione applicata tra gate e bulk si individuano tre regioni di lavoro del dispositivo:

Regione di interdizione

[modifica | modifica wikitesto]La regione di interdizione, anche detta di cut-off, si verifica quando , dove è la tensione tra gate e source, considerando il terminale di source cortocircuitato con l'elettrodo del bulk. In questo caso non si verifica la formazione del canale: il transistor è spento e non vi è passaggio di carica tra gate e source.

Regione lineare

[modifica | modifica wikitesto]La regione lineare, anche detta regione ohmica[2][3] o di triodo, si verifica quando e .

In questo caso il transistor è acceso, e si è creato il canale che permette il passaggio di corrente tra i terminali drain e source controllato dalla tensione VGS. Avendo il canale una componente resistiva, il MOSFET lavora come un resistore

Regione di saturazione

[modifica | modifica wikitesto]La regione di saturazione, anche detta regione attiva,[4][5] si verifica quando e . All'aumentare della tensione tra drain e source, la differenza di potenziale fra il gate e la regione del canale vicina al drain diminuisce, ed il canale viene progressivamente strozzato in prossimità di esso. Tale fenomeno è detto pinch-off, e la strozzatura si verifica nel punto di ascissa , pari alla lunghezza del canale, in cui il potenziale è pari a .[6] La carica di inversione, dunque, diminuisce all'avvicinarsi al terminale di drain, e questo implica che una volta raggiunto il completo strozzamento il valore della corrente che percorre il canale non dipende dalla variazione di , dal momento che la tensione ai capi del canale ohmico rimane costante. Le cariche attraversano quindi la regione svuotata sostenute dal campo elettrico, sicché la corrente dipende solamente dalla tensione , ed il transistor funziona come amplificatore.[6] Quando il transistor lavora in regione di saturazione la corrente dipende quadraticamente dalla tensione tra gate e source:[7]

Simbolo circuitale

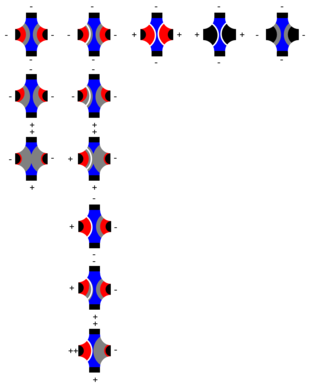

[modifica | modifica wikitesto]I simboli circuitali dei FET sono molteplici, tutti caratterizzati dall'avere i tre terminali, gate, source e drain con un eventuale body aggiuntivo per indicare il substrato disponibile come piedino in rari transistor MOSFET degli anni 1960[senza fonte], identificati da una linea: quella del gate è perpendicolare alle altre due. La connessione del bulk è mostrata da una freccia che punta da P a N, cioè nel caso di un FET a canale p, punta dal bulk al canale. Il contrario accade per il FET a canale n. Nel caso il terminale di bulk non sia mostrato, per il MOSFET si usa il simbolo invertente (un pallino in prossimità del gate) per identificare i pMOS; in alternativa una freccia sul source indica l'output per il nMOS o l'input per il pMOS.

Di seguito il confronto tra i vari simboli di MOSFET e JFET:

|

|

|

|

|

Canale P |

|

|

|

|

|

Canale N |

| JFET | MOSFET enh | MOSFET enh (no bulk) | MOSFET dep | ||

Per i simboli in cui è mostrato il terminale di bulk, esso appare connesso al source: questa è una configurazione tipica, ma non è l'unica possibile. In generale il MOSFET è un dispositivo a quattro terminali.

Tipi

[modifica | modifica wikitesto]

I transistor a effetto di campo si possono distinguere in varie tipi a seconda della differente struttura e composizione: per ogni tipo vi sono vari modelli, differenziati dal modo in cui viene isolato il terminale di gate dal canale.

I tipi principali sono elencati di seguito:

- DEPFET, FET composto da substrato completamente svuotato, è usato come sensore, amplificatore e nodo di memoria.

- DGMOSFET, mosfet con due terminali di gate.

- DNAFET, particolare tipo di FET basato sulla struttura del DNA, usato come biosensore.

- FREDFET, acronimo di Fast Reverse or Fast Recovery Epitaxial Diode FET.

- HEMT, acronimo di High Electron Mobility Transistor, anche detto HFET (heterostructure FET).

- IGBT, acronimo di Insulated-Gate Bipolar Transistor, dispositivo per il controllo della potenza del segnale.

- ISFET, usato per la misura della concentrazione di ioni in una soluzione.

- JFET, acronimo di Junction Field-Effect Transistor, caratterizzato dall'avere tre strati di semiconduttore con drogaggio alternato.

- MESFET, acronimo di Metal–Semiconductor Field-Effect Transistor, dispositivo che sostituisce alla giunzione p-n la barriera di Schottky.

- MODFET, acronimo di Modulation-Doped Field Effect Transistor, usa una struttura a buca di potenziale.

- MOSFET, acronimo di Metal–Oxide–Semiconductor Field-Effect Transistor, usa un isolante tra gate e substrato.

- NOMFET, acronimo di Nanoparticle Organic Memory FET.

- OFET, acronimo di Organic FET, usa un semiconduttore organico.

- BIOFET, i cambiamenti del potenziale di gate sono indotti da un materiale sensibile e dall'interazione con le biomolecole cui fa riferimento il biosensore. Quando la biomolecola si lega al materiale sensibile si verifica un cambiamento della distribuzione di carica elettrica che risulta rilevabile tipicamente con un cambiamento di conduttanza del canale. Un esempio di applicazione sono i COVID-FET[8], biotransistor FET per rilevare la presenza di SARS-Cov2 sfruttando il legame con le proteine Spike.

Note

[modifica | modifica wikitesto]- ^ Computer History - 1960 - Metal Oxide Semiconductor (MOS) Transistor Demonstrated, su computerhistory.org. URL consultato il 4 dicembre 2010.

- ^ C Galup-Montoro & Schneider MC, MOSFET modeling for circuit analysis and design, London/Singapore, World Scientific, 2007, p. 83, ISBN 981-256-810-7.

- ^ Norbert R Malik, Electronic circuits: analysis, simulation, and design, Englewood Cliffs, NJ, Prentice Hall, 1995, pp. 315–316, ISBN 0-02-374910-5.

- ^ PR Gray, PJ Hurst, SH Lewis & RG Meyer, §1.5.2 p. 45, ISBN 0-471-32168-0.

- ^ A. S. Sedra and K.C. Smith, Microelectronic circuits, Fifth Edition, New York, Oxford, 2004, p. 552, ISBN 0-19-514251-9.

- ^ a b Spirito, Pag. 61.

- ^ Spirito, Pag. 62.

- ^ Alessandro Mastrofini, Biosensori per rivelare il virus SARS-CoV2 con transistor FET, su Biomed CuE | Close-up Engineering, 21 luglio 2021. URL consultato il 28 agosto 2021.

Bibliografia

[modifica | modifica wikitesto]- Paolo Spirito, Elettronica digitale, Milano, McGraw-Hill Libri Italia sr., 2006, ISBN 978-88-386-6323-9.

Voci correlate

[modifica | modifica wikitesto]- Transistor 3D

- Giunzione p-n

- Semiconduttore

- Transistor a giunzione bipolare

- MOSFET

- JFET

- CMUT

- IGBT

- Effetto Early

- Transistor Schottky

- Package (elettronica)

Altri progetti

[modifica | modifica wikitesto] Wikibooks contiene testi o manuali sul transistor a effetto di campo

Wikibooks contiene testi o manuali sul transistor a effetto di campo Wikizionario contiene il lemma di dizionario «FET»

Wikizionario contiene il lemma di dizionario «FET» Wikimedia Commons contiene immagini o altri file sul transistor a effetto di campo

Wikimedia Commons contiene immagini o altri file sul transistor a effetto di campo

Collegamenti esterni

[modifica | modifica wikitesto]- FET, in Dizionario delle scienze fisiche, Istituto dell'Enciclopedia Italiana, 1996.

- FET, su sapere.it, De Agostini.

- (EN) field-effect transistor / field-effect transistor electrode, su Enciclopedia Britannica, Encyclopædia Britannica, Inc.

- (EN) Opere riguardanti Field-effect transistors, su Open Library, Internet Archive.

- (EN) field effect transistor, in Free On-line Dictionary of Computing, Denis Howe. Disponibile con licenza GFDL

| Controllo di autorità | LCCN (EN) sh85048099 · GND (DE) 4131472-4 · J9U (EN, HE) 987007531342605171 · NDL (EN, JA) 01150221 |

|---|